Difference between revisions of "Projects:Badge/Documentation/ESP32"

From SHA2017 Wiki

(Created page with "==ESP32== [http://espressif.com/en/media_overview/news/espressif-sponsors-sha2017-badge-project ESP-WROOM-32 module with a 128 Mbit flash] Needs more info!") |

|||

| Line 1: | Line 1: | ||

==ESP32== | ==ESP32== | ||

| − | [http://espressif.com/en/media_overview/news/espressif-sponsors-sha2017-badge-project ESP-WROOM-32 module with a 128 Mbit flash] | + | The [[Projects:Badge|SHA2017Badge]] uses a [http://espressif.com/en/media_overview/news/espressif-sponsors-sha2017-badge-project Special ESP-WROOM-32 module with a 128 Mbit flash] |

| − | + | '''ESP32''' is a series of low cost, low power [https://en.wikipedia.org/wiki/System_on_a_chip system on a chip] [https://en.wikipedia.org/wiki/Microcontroller microcontroller]s with integrated [https://en.wikipedia.org/wiki/Wi-Fi Wi-Fi] & dual-mode [https://en.wikipedia.org/wiki/Bluetooth Bluetooth]. The ESP32 series employs a [https://en.wikipedia.org/wiki/Tensilica Tensilica] Xtensa LX6 microprocessor in both dual-core and single-core variations. ESP32 is created and developed by Espressif Systems, a Shanghai-based Chinese company, and is manufactured by [https://en.wikipedia.org/wiki/TSMC TSMC] using their [https://espressif.com/en/products/hardware/esp32/overview 40 nm process]. It is a successor to the [https://en.wikipedia.org/wiki/ESP8266 ESP8266] microcontroller. | |

| + | |||

| + | == Features == | ||

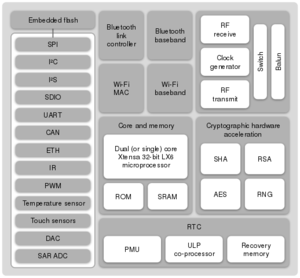

| + | [[File:Espressif ESP32 Function Block Diagram.png|thumb|right|Espressif ESP32 Function Block Diagram]] | ||

| + | Features of the ESP32 include the following: | ||

| + | |||

| + | * CPU: Xtensa Dual-Core 32-bit LX6 microprocessor, operating at 160 or 240 MHz and performing at up to 600 [https://en.wikipedia.org/wiki/Dhrystone DMIPS] | ||

| + | * Memory: 520 KiB SRAM | ||

| + | * Wireless connectivity: | ||

| + | ** Wi-Fi: [https://en.wikipedia.org/wiki/EEE_802.11 802.11] b/g/n/e/i | ||

| + | ** Bluetooth: v4.2 BR/EDR and BLE | ||

| + | * Peripheral interfaces: | ||

| + | ** 12-bit [https://en.wikipedia.org/wiki/Successive_approximation_ADC SAR ADC] up to 18 channels | ||

| + | ** 2 × 8-bit [https://en.wikipedia.org/wiki/Digital-to-analog_converter DACs] | ||

| + | ** 10 × touch sensors | ||

| + | ** Temperature sensor | ||

| + | ** 4 × [https://en.wikipedia.org/wiki/Serial_Peripheral_Interface_Bus SPI] | ||

| + | ** 2 × [https://en.wikipedia.org/wiki/I%C2%B2S I²S] | ||

| + | ** 2 × [https://en.wikipedia.org/wiki/I%C2%B2C I²C] | ||

| + | ** 3 × [https://en.wikipedia.org/wiki/Universal_asynchronous_receiver/transmitter UART] | ||

| + | ** SD/SDIO/MMC host | ||

| + | ** Slave (SDIO/SPI) | ||

| + | ** [https://en.wikipedia.org/wiki/Ethernet Ethernet] MAC interface with dedicated DMA and IEEE 1588 support | ||

| + | ** [https://en.wikipedia.org/wiki/CAN_bus CAN bus] 2.0 | ||

| + | ** IR (TX/RX) | ||

| + | ** Motor [https://en.wikipedia.org/wiki/Pulse-width_modulation PWM] | ||

| + | ** LED [https://en.wikipedia.org/wiki/Pulse-width_modulation PWM] up to 16 channels | ||

| + | ** [https://en.wikipedia.org/wiki/Hall_effect_sensor Hall effect sensor] | ||

| + | ** Ultra low power analog pre-amplifier | ||

| + | * Security: | ||

| + | ** IEEE 802.11 standard security features all supported, including WFA, WPA/WPA2 and WAPI | ||

| + | ** Secure boot | ||

| + | ** Flash encryption | ||

| + | ** 1024-bit OTP, up to 768-bit for customers | ||

| + | ** Cryptographic hardware acceleration: [https://en.wikipedia.org/wiki/Advanced_Encryption_Standard AES], [https://en.wikipedia.org/wiki/SHA-2 SHA-2], [https://en.wikipedia.org/wiki/RSA_(cryptosystem) RSA], [https://en.wikipedia.org/wiki/Elliptic_curve_cryptography elliptic curve cryptography] (ECC), [https://en.wikipedia.org/wiki/Random_number_generator random number generator] (RNG) | ||

| + | * Power Management | ||

| + | ** Internal LDO | ||

| + | ** Individual power domain for RTC | ||

| + | ** 5uA deep sleep current | ||

| + | ** Wake up from GPIO interrupt, timer, ADC measurements, capacitive touch sensor interrupt | ||

| + | |||

| + | Read the full [https://www.espressif.com/sites/default/files/documentation/esp32_datasheet_en.pdf ESP32 Datasheet] for more info. | ||

Revision as of 17:44, 15 June 2017

ESP32

The SHA2017Badge uses a Special ESP-WROOM-32 module with a 128 Mbit flash

ESP32 is a series of low cost, low power system on a chip microcontrollers with integrated Wi-Fi & dual-mode Bluetooth. The ESP32 series employs a Tensilica Xtensa LX6 microprocessor in both dual-core and single-core variations. ESP32 is created and developed by Espressif Systems, a Shanghai-based Chinese company, and is manufactured by TSMC using their 40 nm process. It is a successor to the ESP8266 microcontroller.

Features

Features of the ESP32 include the following:

- CPU: Xtensa Dual-Core 32-bit LX6 microprocessor, operating at 160 or 240 MHz and performing at up to 600 DMIPS

- Memory: 520 KiB SRAM

- Wireless connectivity:

- Wi-Fi: 802.11 b/g/n/e/i

- Bluetooth: v4.2 BR/EDR and BLE

- Peripheral interfaces:

- 12-bit SAR ADC up to 18 channels

- 2 × 8-bit DACs

- 10 × touch sensors

- Temperature sensor

- 4 × SPI

- 2 × I²S

- 2 × I²C

- 3 × UART

- SD/SDIO/MMC host

- Slave (SDIO/SPI)

- Ethernet MAC interface with dedicated DMA and IEEE 1588 support

- CAN bus 2.0

- IR (TX/RX)

- Motor PWM

- LED PWM up to 16 channels

- Hall effect sensor

- Ultra low power analog pre-amplifier

- Security:

- IEEE 802.11 standard security features all supported, including WFA, WPA/WPA2 and WAPI

- Secure boot

- Flash encryption

- 1024-bit OTP, up to 768-bit for customers

- Cryptographic hardware acceleration: AES, SHA-2, RSA, elliptic curve cryptography (ECC), random number generator (RNG)

- Power Management

- Internal LDO

- Individual power domain for RTC

- 5uA deep sleep current

- Wake up from GPIO interrupt, timer, ADC measurements, capacitive touch sensor interrupt

Read the full ESP32 Datasheet for more info.